# **ARTICLE**

Received 24 Sep 2012 | Accepted 21 Mar 2013 | Published 30 Apr 2013

DOI: 10.1038/ncomms2785

# Large-scale organic nanowire lithography and electronics

Sung-Yong Min<sup>1</sup>, Tae-Sik Kim<sup>1</sup>, Beom Joon Kim<sup>2</sup>, Himchan Cho<sup>1</sup>, Yong-Young Noh<sup>3</sup>, Hoichang Yang<sup>4</sup>, Jeong Ho Cho<sup>2</sup> & Tae-Woo Lee<sup>1</sup>

Controlled alignment and patterning of individual semiconducting nanowires at a desired position in a large area is a key requirement for electronic device applications. High-speed, large-area printing of highly aligned individual nanowires that allows control of the exact numbers of wires, and their orientations and dimensions is a significant challenge for practical electronics applications. Here we use a high-speed electrohydrodynamic organic nanowire printer to print large-area organic semiconducting nanowire arrays directly on device substrates in a precisely, individually controlled manner; this method also enables sophisticated large-area nanowire lithography for nano-electronics. We achieve a maximum field-effect mobility up to  $9.7~\rm cm^2~V^{-1}~s^{-1}$  with extremely low contact resistance ( $<5.53~\Omega$ cm), even in nano-channel transistors based on single-stranded semiconducting nanowires. We also demonstrate complementary inverter circuit arrays comprising well-aligned p-type and n-type organic semiconducting nanowires. Extremely fast nanolithography using printed semiconducting nanowire arrays provide a simple, reliable method of fabricating large-area and flexible nano-electronics.

<sup>&</sup>lt;sup>1</sup> Department of Materials Science and Engineering, Pohang University of Science and Technology (POSTECH), San 31, Hyoja-dong, Nam-gu, Pohang, Gyungbuk 790-784, Republic of Korea. <sup>2</sup> SKKU Advanced Institute of Nanotechnology (SAINT) and Center for Human Interface Nano Technology (HINT), Sungkyunkwan University, Suwon 440-746, Republic of Korea. <sup>3</sup> Department of Energy and Materials Engineering, Dongguk University, 26, Pil-dong, 3-ga, Jung-gu, Seoul 100-715, Republic of Korea. <sup>4</sup> Department of Advanced Fiber Engineering, Inha University, Incheon 402-751, Republic of Korea. Correspondence and requests for materials should be addressed to T. -W. L. (email: twlee@postech.ac.kr).

rocesses have been developed that use inorganic nanomaterials for fabricating high-performance, large-area flexible electronic devices <sup>1-3</sup>. In particular, inorganic semiconductor nanowires (NWs) have been extensively studied because of their intriguing physical properties and great potential as building blocks for nanoscale electronics and optoelectronics<sup>4,5</sup>. Despite the many advantages of NWs, a reliable process for large-scale and controllable assembly of highly aligned NW parallel arrays based on 'individual control (IC)' of NWs must be developed, because inorganic NWs are mostly grown vertically on substrates and thus have been transferred to the target substrates by any of several non-IC methods, such as the random dispersion method with disordered alignment<sup>4</sup>, and contact-printing technologies with unidirectional massive alignment<sup>5</sup>. In contrast to the significant efforts and in-depth research on inorganic NW devices, devices based on 'organic semiconducting' NWs (OSNWs)6 have not been studied intensively, possibly because of the lack of a reliable IC process to fabricate highly aligned OSNW arrays<sup>7-11</sup>, and to the lower charge-carrier mobility of OSNWs compared with inorganic semiconducting NWs. However, as organic semiconductors have many advantages, such as solution processibility, simplicity of designing molecules to tune electronic properties and the possibility of large-scale synthesis and multi-component systems at low cost, they are also promising for use in flexible electronic and optoelectronic devices 6,7,12,13. For practical device application of OSNWs, they should be individually controlled for alignment and patterning at desired positions and orientations, and the number of OSNWs must be exactly defined. However, this objective has not yet been achieved to date for flexible organic nano-electronics, despite the significance. In addition, OSNWs should be fabricated directly on the device substrate without requiring any additional transfer process. Therefore, reliable and controllable processes to satisfy these requirements will provide large-area OSNW arrays and their applications to NW lithography, and electronic devices. In particular, large-scale organic NWs (ONWs) with circular shape can provide a facile route to nanolithography in large area. Existing inorganic NW lithography techniques to prepare nano-patterns for electronic devices use the randomly dispersed metal NW itself<sup>14,15</sup> or use randomly dispersed semiconductor NW as an etch mask<sup>16</sup>. However, with these non-IC processes, the position and orientation of individual NWs and nano-patterns are difficult to control, and thus sample-to-sample variation of device performance may not be avoided.

Here we report (i) high-speed, large-area printing of highly aligned, individually controlled OSNWs for NW electronics: the exact numbers of wires, their orientations and their dimensions are controlled directly on the device substrate without any transfer printing process; (ii) large-area ONW lithography (ONWL) using the highly aligned, individually controlled OSNWs; (iii) application of ONWL to fabricate large-area OSNW electronic devices with nanoscale channel length: we achieved unprecedented high field-effect mobility ( $\mu_{\text{FET}}$ ) from nanochannel ONW transistors with extremely low contract resistance; and (iv) the large-area complementary inverter circuit arrays comprising well-aligned p-type and n-type OSNWs. First, we used our own home-built ONW printer to print highly aligned, individually controlled OSNWs at desired positions on device substrates and to fabricate large-area OSNW transistor arrays. Then we used the aligned ONWs as a shadow mask to generate large-area nanoscale patterns very quickly, and fabricated largearea OSNW transistor arrays with nanoscale channel length and complementary inverter arrays, using well-aligned p- and n-type polymer semiconductor NWs; this scalable method can overcome the drawbacks of conventional electron-beam lithography, which

is relatively slow, complicated and expensive. As our electrohydrodynamic ONW printing (ONP) technique can align the ONWs in continuous jet mode, unlike conventional dropon-demand-type jet printing techniques<sup>17</sup>, 'perfect circular' NWs can be generated. We obtained highly aligned ONWs (or organic nanofibres) from poly(9-vinyl carbazole) (PVK), semiconducting poly(3-hexylthiophene) (P3HT) and poly{[N, N'-bis(2-octyldodecyl)-naphthalene-1,4,5,8-bis(dicarboximide)-2, 6-divl]-alt-5,5'-(2,2'-bithiophene)} (Polvera ActivInk N2200); we used PVK as a shadow mask for ONWL and P3HT as the semiconductor layer in transistors. By combining NW printing and ONWL, we achieved a very high maximum  $\mu_{\text{FET}}$ up to  $9.7 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  (average  $\mu_{\text{FET}} \sim 3.8 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ) in P3HT NW transistors, even with a very short channel length of  $\sim$  300 nm with extremely low contract resistance (<5.53  $\Omega$  cm). We finally demonstrated large-area complementary inverter circuit arrays comprising well-aligned p-type and n-type OSNWs.

#### Results

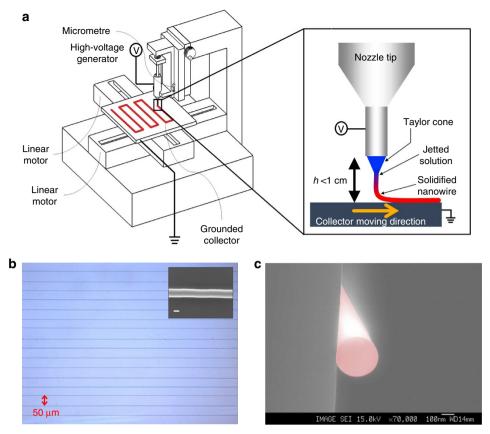

Fabrication of aligned ONWs. Our home-built ONW printer (Fig. 1a) consists of a high-speed linear motor x-y stage, a flat grounded collector, a micrometre to control the tip-to-collector distance, a nozzle (tip inner diameter:  $\sim 100 \, \mu \text{m}$ ), a syringe pump and a high-voltage generator. To form the ONWs, an electrohydrodynamic process is used like, similar to electrospinning<sup>9–11</sup>. This employs the electrostatic force to stretch the viscous polymer solution into NW: a viscous polymer solution is injected into the nozzle and high-voltage is applied to the nozzle. Because of the electric field, the repulsive force within the charged solution and the attractive force between the solution at the nozzle tip and a grounded collector shape the droplet into a Taylor cone at the nozzle tip. When these forces are larger than the surface tension of solution, a jet is ejected from the tip of the Taylor cone and deposited onto the grounded collector with rapid elongation. Unlike conventional electrospinning processes, we approached the nozzle tip near to the collector (less than 1 cm), which resulted in suppression of the chaotic whipping motion of jetted polymer solution: as the tip-to-collector distance decreases, perturbation of jetted solution decreases<sup>18</sup>. By moving the motorized x-y stage while the NWs are ejected, we can align the ONWs with desired orientation.

To verify the capacity of ONP to print ONWs quickly with precise alignment, we used a solution of 3.96 wt% PVK in styrene. PVK NWs were printed while the collector moves laterally at  $13.3 \,\mathrm{cm}\,\mathrm{s}^{-1}$  (maximum speed  $100 \,\mathrm{cm}\,\mathrm{s}^{-1}$ ). The resulting patterns had totally parallel orientation; the NWs had regular spacing of  $50 \,\mu\text{m}$  and diameter of  $289.26 \pm 35.37 \,\text{nm}$  (Fig. 1b). The NW diameter can be controlled by adjusting polymer concentration (Supplementary Fig. S1a,b). Therefore, the ONW diameter can be further reduced to <100 nm (Supplementary Fig. S1c). Optical microscope (Fig. 1b) and scanning electron microscope images (inset of Fig. 1b) demonstrate the formation of uniform and continuous ONWs. The tip-to-collector distance was  $\sim 2.5$  mm; if it was < 2.5 mm, the jets arrived at the substrate in liquid form and merged readily without forming solid-state wires, because the solvent did not have sufficient time to evaporate. In cross section, the PVK NWs were perfectly circular (Fig. 1c), implying successful formation of ONWs. When the collector was stationary, self-entanglement of NWs ('local spiraling') was observed (Supplementary Fig. S2); this is further evidence of successful formation of wires, because it occurs when the polymer jet is fully solidified. Aligned PVK NWs (Fig. 1b) were formed by writing a long single strand of wire laterally. The total length of the aligned NWs was as long as  $\sim$  15 m; printing them required only  $\sim$  2 min.

**Figure 1 | Organic nanowire printing.** (a) Schematic diagram of ONW printer and NW printing process. (b) Optical micrograph of well-aligned PVK NWs. The diameter of PVK NW is 290 nm (inset, scale bar, 200 nm). (c) Field emission scanning electron microscope image showing cross section of well-aligned PVK NW, which forms a perfect circle.

Highly aligned ONW field-effect transistors. When fabricating transistors using OSNWs, forming the wires at the desired position in an individually controlled fashion is usually very diffi-cult<sup>6,7,9–12</sup>. Using ONP, we fabricated well-aligned P3HT NW field-effect transistors (FETs) very simply and quickly. P3HT was used as the active material for large-area organic wire electronic device arrays, and poly(ethylene oxide) (PEO) (Aldrich,  $M_{\rm w} \sim 400,000$ ) was added to the P3HT solution (P3HT:PEO = 80:20, w/w) to increase its viscosity. To fabricate the OSNW FETs, we printed the blend wires on the Si/SiO<sub>2</sub> (100 nm) substrate and deposited Au (100 nm) for the source and drain electrode. Although the Si/SiO<sub>2</sub> substrate has an insulating surface, ONWs can be successfully printed by ONP, because the insulating layer is very thin enough to maintain a high electric field between the nozzle tip and the grounded collector. Therefore, even if the substrate has a thin insulating layer, we can print the ONWs on any kind of substrate: on an insulating SiO<sub>2</sub> layer (300 nm) and even a paper (108 µm; Supplementary Fig. S3).

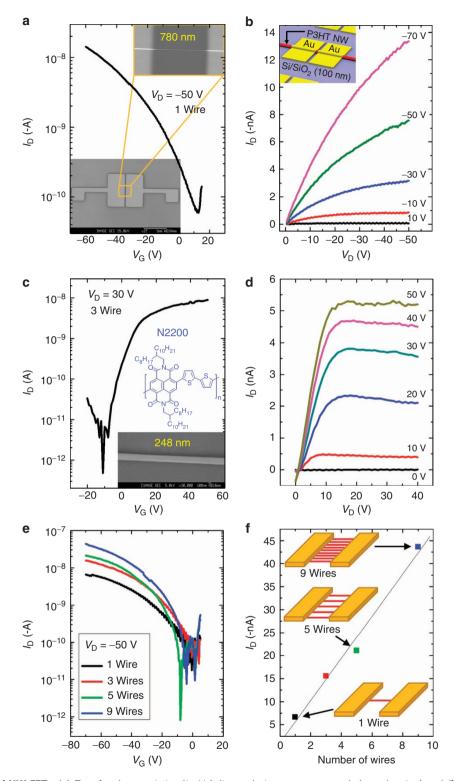

The P3HT:PEO-blend NWs were successfully printed between source and drain electrodes (Fig. 2a inset). The drain-current ( $I_{\rm D}$ ) to gate voltage ( $V_{\rm G}$ ) transfer characteristic measured at drain voltage  $V_{\rm D}=-50\,{\rm V}$  for  $V_{\rm G}$  swept from 15 to  $-60\,{\rm V}$  shows the behaviour of typical p-type FETs (Fig. 2a). The gate effect was also observed in the output ( $I_{\rm D}-V_{\rm D}$ ) characteristic (Fig. 2b), which means that an effective channel was formed despite the presence of PEO.

In NW FETs using a thin-film gate dielectric,  $\mu_{\rm FET}$  is calculated as  $^{19}$  :

$$\mu_{\text{FET}} = \frac{L^2 g_{\text{m}}}{V_{\text{D}} C} = \frac{L^2}{V_{\text{D}} C} \cdot \frac{d(I_{\text{D}})}{d(V_{\text{G}})},\tag{1}$$

where  $L = 50 \,\mu\text{m}$  is its channel length and C is its capacitance (F) determined using the cylinder-on-plate model<sup>20</sup>,

$$C = \frac{2\pi\varepsilon_0\varepsilon_r L}{\cosh^{-1}\left(\frac{h+r}{r}\right)},\tag{2}$$

where  $\varepsilon_0 = 8.85 \times 10^{-12} \,\mathrm{F m^{-1}}$  is vacuum permittivity,  $\varepsilon_r = 3.9$  is the relative permittivity of the SiO<sub>2</sub> gate dielectric layer,  $h = 100 \,\mathrm{nm}$  is the thickness of the SiO<sub>2</sub> gate dielectric layer and r is NW radius ( $\sim 275 \,\mathrm{nm}$  for the NW with 30% PEO and  $\sim 780 \,\mathrm{nm}$  for P3HT blend NW with 20% PEO).

The calculated  $\mu_{\rm FET}$  of the P3HT:PEO-blend (80:20, w/w) NW FET (bottom-gate) was  $0.015\,{\rm cm^2\,V^{-1}\,s^{-1}}$ , which is comparable to that of pure P3HT NW FET<sup>11</sup> ( $\mu_{\rm FET}=0.03\,{\rm cm^2\,V^{-1}\,s^{-1}}$ ). In P3HT:PEO-blend (70:30, w/w) NW FETs, NWs were more easily printed due to increased viscosity, but  $\mu_{\text{FET}}$  was lower: 0.0047 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> (Supplementary Fig. S4a), because insulating PEO phases in a P3HT matrix hinder charge transport and block the stacking of P3HT chains; these effects degrade  $\mu_{\text{FET}}$ . To increase electrical properties of NW FETs, we also demonstrated a top-gated device using poly(methyl methacrylate) (PMMA) as a gate dielectric (Supplementary Fig. S4b). The calculated  $\mu_{\text{FET}}$  of the top-gated P3HT blend NW FET with 30% PEO was  $0.012 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , similar to the bottom-gated P3HT:PEO-blend (80:20, w/w) NW FET. We have also examined the bias stress stability of P3HT:PEOblend NW FETs (Supplementary Fig. S4c,d and Supplementary Note S1). After initial gate bias stress for 1 h to fill the trap states,  $\mu_{\rm FET}$ , on/off ratio and threshold voltage ( $V_{\rm th}$ ) shift were saturated and then did not show significant degradation for 11h.

We fabricated *n*-type NW FETs by ONP using a N2200: PEO-blend (80:20, w/w) as an *n*-type semiconducting polymer.

**Figure 2 | Highly aligned NW FETs.** (a) Transfer characteristics ( $I_D$ – $V_G$ ) (inset: device appearance and channel region) and (b) output ( $I_D$ – $V_D$ ) characteristics of P3HT blend NW FET with 20% PEO (inset: device structure). (c) Transfer characteristics and (d) output characteristics of poly{[N, N'-bis(2-octyldodecyl)-naphthalene-1,4,5,8-bis(dicarboximide)-2,6-diyl]-alt-5,5'-(2,2'-bithiophene)} (N2200) blend NW FET with 20% PEO. (e) Transfer characteristics of P3HT blend NW FET with 30% PEO at different numbers of wires. (f) Maximum on-current versus the number of wires.

The *n*-type NW FET (bottom-gate) showed typical *n*-type transfer and output characteristics (Fig. 2c,d) with the electron  $\mu_{\text{FET}}$  of 0.012 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. The N2200:PVK-blend (80:20, w/w) exhibited electron  $\mu_{\text{FET}}$  of 0.03 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> (Supplementary Fig. S5), which is slightly lower than that of a pure N2200

thin-film FET in a bottom-gate geometry with a  $SiO_2$  gate dielectric  $(\mu_{\rm FET}=0.06\,{\rm cm^2\,V^{-1}\,s^{-1}})^{21}$ . Achievement of both well-aligned organic *p*-channel and *n*-channel NW FETs provides fundamental resources for various large-area electronic applications.

Another important advantage of ONP is that the number of aligned NWs can be easily controlled. The P3HT:PEO-blend (70:30, w/w) NW FETs with one, three, five and nine wires were fabricated. According to the  $I_{\rm D}-V_{\rm G}$  relationship (Fig. 2e), the maximum oncurrent level increased linearly with the number of wires in FETs (4.6  $\times$  10  $^{-9}$  A per wire) (Fig. 2f); this relationship indicates that device characteristics can be controlled by adjusting the number of wires with the ONP technique. Calculated  $\mu_{\rm FET}$  values of NW FETs were almost the same irrespective of the number of wires (0.0047, 0.0054, 0.0053 and 0.0039 cm $^2$  V  $^{-1}$  s  $^{-1}$  for one, three, five and nine wires, respectively).

According to transmission electron microscopy (Supplementary Fig. S6a) and elemental analysis results (Supplementary Fig. S6b,c and Supplementary Note S2), a P3HT:PEO-blend NW has a coreshell structure along the wire axis. The origin of the core-shell structure of printed NW is explained by phase separation of polymer blends, which can be caused by the incompatibility or the large solubility parameter difference in solution<sup>22</sup>. On the basis of grazing-incidence X-ray diffraction (GIXRD) and polarized photoluminescence analysis for the aligned OSNWs, we found that the aligned NWs had long-range ordered nano-domains along the wire axis (Supplementary Figs S7 and S8, and Supplementary Notes S3 and S4). This is mainly related to the directed selfassembly between  $\pi$ -conjugated backbone chains extended along the wire axis by the tip-to-collector electric field, during jetting. It was also found that the extended P3HTs had strong intermolecular  $\pi$ -overlap as a result of ultraviolet-visible spectroscopy analysis (Supplementary Fig. S8a). Such extended orientation of P3HTs along the source/drain electrode and enhanced intermolecular  $\pi$ – $\pi$ overlap facilitates charge transport in NW FETs. However, phase separation between P3HT and PEO is not perfect. Small randomly distributed PEO-rich phases occur very sparsely inside the P3HT core (red circle in Supplementary Fig. S6a,b). These small phases scatter the charge transport in the channel and cause the variation of  $\mu_{\text{FET}}$  in P3HT:PEO-blend NW FETs.

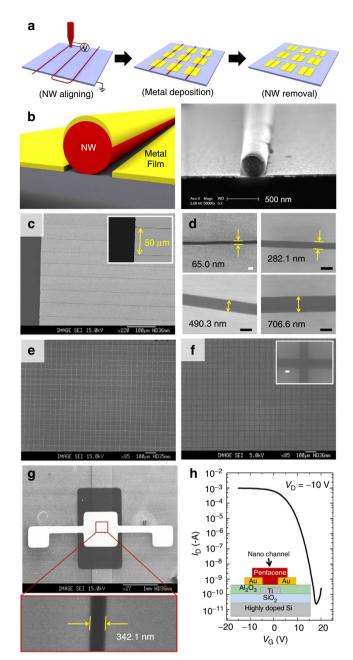

ONWL and nano-channel FETs. We also applied ONP to form large-area nano-sized patterns. Using ONWL, well-aligned nanogap metal patterns can be fabricated very quickly at a desired position. In the ONWL process (Fig. 3a), aligned PVK NWs fabricated using ONP are used as a shadow mask of deposited metal films. After printing PVK NWs on a substrate, followed by deposition of metal films, the ONWs are removed either by sonicating the solvent to dissolve them, or by using adhesive tapes to detach them. As the contact area between PVK NWs and substrate is minimal, and as the deposited metal film is thinner than the NW radius (~150 nm), resulting in no physical contact between the NW mask and deposited metal film, wires can be easily removed (Fig. 3b). Conventional drop-on-demand-type jetprinting techniques produce only continuous lines with very low aspect ratio formed via the connection of each drop (not circular wires) so that the lift-off of printed mask lines to achieve nanoscale patterns is quite difficult. Using ONWL, parallel patterns of gold nano-gaps were successfully formed, which had the same orientation and spacing as those of PVK NWs (Fig. 3c). The size of the gaps can be easily controlled by adjusting NW diameter (Fig. 3d).

ONWL can be used to fabricate complicated patterns on large area simply. With perpendicularly aligned NW patterns (Fig. 3e), grid-structured nano-gap patterns were obtained over an area of  $\sim 300\,\mathrm{cm^2}$  on an 8-inch wafer (Fig. 3f and Supplementary Fig. S9). Furthermore, ONWL can be also used to fabricate organic nano-gap pattern and to fabricate nano-pattern on flexible substrate. Using ONWL, aluminum tris (8-hydroxy-quinoline) (Alq<sub>3</sub>) layer was successfully patterned with the gap

**Figure 3 | ONWL to fabricate the nano-gap metal pattern.** (a) Schematic illustration of the process for ONWL. (b) Schematic illustration (left) and scanning electron microscope image (right) showing the cross section of an ONW after metal deposition process in ONWL. There is no contact between NW and deposited metal film. (c) Parallel array of nano-sized gold gap with 50- $\mu$ m spacing. (d) Size of gold gap can be controlled by diameter of NWs. Scale bar, 100 nm (white), 500 nm (black). (e) Perpendicular pattern of PVK NWs with 50- $\mu$ m spacing and (f) corresponding grid-structured pattern of gold nano-gap (inset: region of intersection, scale bar, 200 nm). (g) Device appearance and nano-sized electrode gap of pentacene thin-film FET with nano-channel. (h) Transfer characteristic ( $I_D - V_G$ ) of pentacene thin-film FET (inset: device structure).

width of  $\sim$  350 nm (Supplementary Fig. S10). When ONWs were printed on flexible polyarylate substrate, they were easily detached by adhesive tape after metal deposition and nano-sized electrode gap patterns were formed (Supplementary Fig. S11). It means that ONWL is very applicable to fabricate the flexible nano-electronics. Therefore, ONWL is a potential alternative method to

replace E-beam lithography, which has been usually used to fabricate the nano-patterns.

ONWL can be used to fabricate nano-channel transistors. Using the nano-gap pattern as an electrode gap, pentacene thin-film transistors with nano-channels were fabricated. A nano-gap of  $\sim 340\,\mathrm{nm}$  was successfully formed (Fig. 3g). The calculated  $\mu_{\mathrm{FET}}$  was  $0.041\,\mathrm{cm^2\,V^{-1}\,s^{-1}}$  and the on/off current ratio was very high:  $4.18\times10^7$  (Fig. 3h). This result in the nano-channel device is comparable with general properties of bottom-contact pentacene thin-film transistors  $^{23}$ .

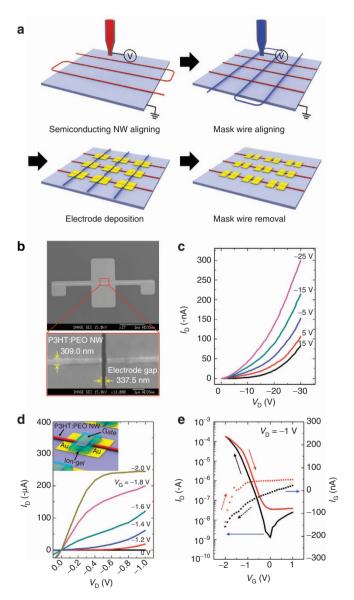

By combining ONP and ONWL, we fabricated organic FETs with nanoscale channel length and channel width (Fig. 4a). ONP produced well-aligned P3HT:PEO-blend NWs as the active

Figure 4 | Organic FET with nano-channel length and width. (a)

Schematic illustration of the process to fabricate organic FET with nanoscale channel length and channel width. **(b)** Scanning electron microscope images of P3HT:PEO-blend (70:30, w/w) NW and nano-sized electrode gap. **(c)** Output characteristics ( $I_D - V_D$ ) of P3HT blend NW FET with nanochannel length. **(d)** Output characteristics (inset: device structure) and **(e)** transfer characteristic ( $I_D - V_G$ ) (solid line) and gate current versus gate voltage ( $I_G - V_G$ ) characteristics (dot line) of P3HT:PEO-blend (70:30, w/w) NW and nano-channel FET based on the polyelectrolyte gate dielectric.

channel, and ONWL produced a gold electrode with a nanogap on top of them (Fig. 4b). In these FETs,  $I_{\rm D}$  increased linearly with  $V_{\rm D}$  and showed no saturation regime (Fig. 4c); this lack of a saturation regime is due to the short channel effect <sup>15,24</sup>, which occurs in FETs that have sub-micrometre channel length. If the magnitude of  $V_{\rm D}$  was  $\geq$  30 V, the device broke down as the channel length is so short. Calculated  $\mu_{\rm FET}$  was 0.0093 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>.

To reduce the operating voltage of ONW FETs, highcapacitance ion-gel polyelectrolyte was used as a gate dielectric material. Ion-gel films were formed on the P3HT:PEO-blend NW by gelation of poly(styrene-b-methylmethacrylate-b-styrene) (PS-PMMA-PS) triblock copolymer in an ionic liquid, 1-ethyl-3-methylimidazolium bis(trifluoromethylsulfonyl)imide<sup>25</sup>; in the single-NW FET based on ion-gel (Fig. 4d inset),  $\mu_{\text{FET}}$  and the oncurrent were dramatically enhanced ( $\mu_{\rm FET} \sim 3.67 \, {\rm cm^2 \, V^{-1} \, s^{-1}}$ ,  $I_{\rm on} \sim 1.81 \times 10^{-4} \, {\rm A}$ ) compared with SiO<sub>2</sub> gate dielectric device (Fig. 4d,e), in spite of low  $V_{\rm D}$  ( -1 V) and  $V_{\rm G}$  ( -2 V); the on/off current ratio was also increased (to  $1.38\times10^5$ ); the best device showed  $\mu_{\rm FET}$  up to 9.7 cm<sup>2</sup> V  $^{-1}$  s  $^{-1}$  (Supplementary Fig. S12). Furthermore, a saturation regime was observed, which did not appear in SiO<sub>2</sub> gate dielectric devices. These observations indicate that the short channel effect was dramatically reduced in the iongel-gated FETs. This apparent reduction of operating voltage occurs, because the ionic electrolyte introduces a large number of charge carriers into the channel. In accumulation mode, electrical double layers are formed at the interfaces of the gate-ionic electrolyte and the ionic electrolyte-semiconductor<sup>26</sup>, and electrochemical doping occurs because of penetration of ions into the semiconductor<sup>27</sup>. Unlike typical insulating materials, no potential drop occurs in ionic electrolytes; hence, a large number of holes are induced at very low  $V_G$ . These results are consistent with previous reports<sup>25,27</sup>. Extremely low contact resistance  $(<5.53\,\Omega\,\text{cm})$  also contributes to the remarkable reduction of short channel effect (Supplementary Fig. S13 and Supplementary Note S5).

To calculate  $\mu_{\text{FET}}$  in ion-gel-gated NW FETs, we used two different equations: the conventional thin-film FET equation<sup>21,23</sup> and the equation based on the gate-displacement current and induced charge density<sup>28,29</sup>. First,  $\mu_{\text{FET}}$  was calculated from the simple 'thin-film FET model' (equation 3)<sup>21,23</sup>.

$$\mu_{\text{FET}} = \frac{2L}{W \cdot C} \cdot \left(\frac{d(I_{\text{D}}^{1/2})}{d(V_{\text{G}})}\right)^2 \tag{3}$$

where W is the channel width. However, this equation is used for FET device with a two-dimensional (2D) metal-insulator semiconductor geometry and is derived on the basis of gradual channel approximation (refer to Supplementary Table S1, Supplementary Fig. S14 and Supplementary Note S6). It also gave unacceptably high values (average  $\mu_{\rm FET}$ :  $\sim 31.00~{\rm cm}^2~{\rm V}^{-1}~{\rm s}^{-1}$ ) for our devices. Therefore, thin-film FET model is not valid for the ionic-electrolyte-gated NW FET.

Instead of thin-film FET model,  $\mu_{\text{FET}}$  can be computed using gate-displacement current and induced carrier density  $(P_i)$ ,  $^{28,29}$

$$\mu_{\text{FET}} = \frac{L}{W} \cdot \frac{I_{\text{D}}}{V_{\text{D}} \cdot eP_{\text{i}}} \tag{4}$$

where e is the elementary charge. The  $\mu_{\rm FET}$  calculated from gate-displacement current gave more reasonable values (average  $\mu_{\rm FET}$ :  $\sim 3.8~{\rm cm^2~V^{-1}~s^{-1}}$ ) than that calculated from equation (3). Although the induced carrier density is inversely proportional to  $\mu_{\rm FET}$ , the calculated  $\mu_{\rm FET}$  is much higher than those of general P3HT FET devices (Supplementary Table S1), because the large induced hole density fills the trap of the P3HT channel and smoothes the electrostatic potential variation that occurs in the

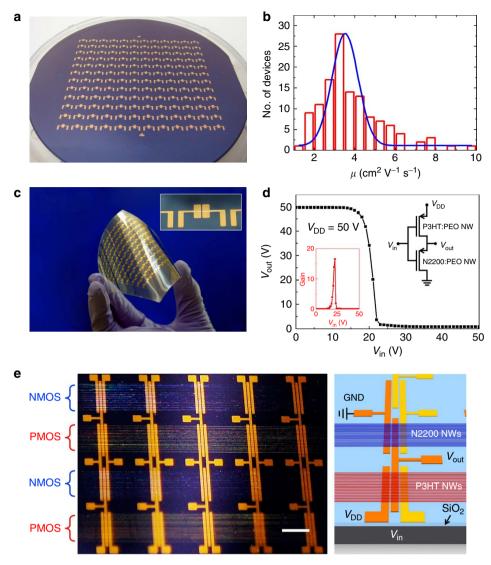

Figure 5 | Large-area single P3HT:PEO-blend NW FET and complementary inverter circuit arrays. (a) Large-area single P3HT:PEO-blend (70:30, w/w) NW FET array (7 cm  $\times$  7 cm) with  $\sim$  300-nm channel length (144 bottom-contact devices). (b) Histogram of the mobility for large-area P3HT:PEO-blend NW FET array with an average of  $3.8 \pm 1.6$  cm<sup>2</sup> V  $^{-1}$  s  $^{-1}$ . (c) Large-area single P3HT:PEO-blend NW FET array on polyarylate (PAR) substrate. (d) Input-output voltage characteristic for complementary inverter circuit based on P3HT:PEO-blend NWs and N2200:PEO-blend NWs (inset: gain characteristics). (e) Optical image of inverter array (left, scale bar, 2 mm) and schematic illustration of an inverter (right).

channel due to trapped charges<sup>29</sup>. In addition, we found that the core-shell structure of P3HT:PEO-blend NWs and extended chain orientation of P3HT along the wire axis contributed to the high  $\mu_{\rm FET}$  of ion-gel-gated NW FETs (Supplementary Figs S6–S8, S15 and S16, and Supplementary Notes S7 and S8).

We achieved a large-area (7 cm  $\times$  7 cm) NW FET array on a 4-inch wafer. This array consists of 144 short-channel FETs that use a continuous single-stranded P3HT:PEO-blend (70:30, w/w) NW (Fig. 5a). ONWL was used to form source/drain gaps  $\sim$  300 nm, and ion-gel was used as the gate dielectric material. Fabricating the single strand of P3HT NW on the wafer scale array took only  $\sim$  7 s. The figures of distribution of the field-effect mobility and maximum on-current (Fig. 5b and Supplementary Fig. S17) show an extremely high  $\mu_{\rm FET}$  of 9.7 cm<sup>2</sup> V  $^{-1}$  s  $^{-1}$  (average  $\mu_{\rm FET}=3.8\pm1.6$  cm<sup>2</sup> V  $^{-1}$  s  $^{-1}$ ), an extraordinarily high average current level of 0.31  $\pm$  0.13 mA and a high average on/off current ratio (1.70  $\times$  10<sup>6</sup>). We also used ONP to fabricate a large-area NW transistor array on a flexible plastic substrate (polyarylate; Fig. 5c).

We finally fabricated the complementary inverter array using

well-aligned P3HT:PEO-blend NWs and N2200:PEO-blend NWs (Fig. 5d). The photograph of inverter arrays based on printed NWs is shown in Fig. 5e. A number of N2200:PEO-blend (70:30, w/w) NWs and P3HT:PEO-blend (70:30, w/w) NWs were aligned on the pre-patterned Ti/Au electrodes with  $L=50\,\mu \rm m$  on a Si/SiO2 (100 nm) substrate. The transistor output currents were readily matched by controlling the number of NWs using ONP. The NW complementary inverter showed the typical switching characteristic with gain of  $\sim$  17. The dynamic switching behaviour of P3HT/N2200 NW complementary inverters was also demonstrated (Supplementary Fig. S18 and Supplementary Note S9).

# Discussion

We first demonstrated practical large-area electronic device applications of individually-controlled OSNWs using ONP, which can be used to print, align and pattern circular ONWs in desired positions and orientations directly on large-area device

substrates. We also developed a large-area ONWL technique to fabricate nano-electronic devices quickly; this technique has the potential to replace conventional E-beam lithography. By combining ONP and ONWL, we fabricated ONW FETs with nanometer channel length in large area, which exhibited unprecedented maximum  $\mu_{\rm FET}$  of  $9.7\,{\rm cm^2\,V^{-1}\,s^{-1}}$  (average  $\mu_{\rm FET} \sim 3.8 \, {\rm cm}^2 \, {\rm V}^{-1} \, {\rm s}^{-1}$ ), high on/off current ratio ( $\sim 10^6$ ) and extremely low contact resistance ( $\sim 5.53 \,\Omega$  cm). ONP and ONWL can be applied to fabricate large-area nano-structured electronic device arrays very simply and quickly. Moreover, we demonstrated large-area complementary inverter circuit arrays composed of highly aligned p-type and n-type OSNWs. Although inverters with randomly oriented ONWs30 were previously introduced, our result demonstrates the first arrays of complementary inverters in which the orientation, position and numbers of ONWs are well-controlled individually in large area. Our strategy to fabricate ONWs in an individually-controlled fashion and their large-area nano-electronic devices in a precisely controlled manner is a promising approach to realize large-area flexible nano-electronics and provides important bases for future textile electronics using long-stranded wires or fibres.

#### Methods

**Equipment setup.** The ONW printer consists of a syringe pump (NanoNC) mounted vertically over the collector, a gas-tight syringe (Hamillton), a 25–32 gauge stainless steel nozzle, a micrometre to control the tip-to-collector distance, a high-voltage generator (NanoNC) and a grounded flat-type collector ( $20 \, \mathrm{cm} \times 20 \, \mathrm{cm}$ ) moved by a linear motor stage (Yaskawa).

**Fabrication of aligned PVK NW**. PVK ( $M_{\rm w}\sim 1,100,000$ , Aldrich) in styrene solution (37.5 mg ml $^{-1}$ ) was injected through the metal nozzle at a feed rate of 500 nl min $^{-1}$ . For production of PVK NWs, the ONW printer was used; 3–4 kV was applied to the nozzle and tip-to-collector distance was set at 2.5 mm. While the NW was being collected on the substrate, the collector moved in a zigzag at 13.3 cm s $^{-1}$ .

**Highly aligned NW FET and complementary inverter**. P3HT (Regioregularity  $\sim 90\%,\ M_{\rm w} \sim 45,570,\ {\rm Aldrich})$  and PEO ( $M_{\rm w} \sim 400,000,\ {\rm Aldrich})$  were used to prepare 70:30 and 80:20 (w/w) blend solutions of P3HT:PEO. Trichloroethylene (TCE) and chlorobenzene were mixed in appropriate ratio and used as the cosolvent of the P3HT:PEO-blend solution. The blended P3HT solution was injected into the metal nozzle and P3HT:PEO-blend NWs were fabricated and aligned on the substrate using the ONW printer. To fabricate the N2200:PEO-blend NWs, the blend solution of N2200 (Polyera) and PEO was prepared using TCE and chlorobenzene as the cosolvent. A bit of isotactic polystyrene ( $M_{\rm w} \sim 400,000,\ {\rm Aldrich}; \sim 1\ {\rm wt}\%$  of PEO) was added into solution, and then N2200:PEO-blend NWs were fabricated using our ONW printer.

For FET fabrication, highly doped silicon wafers and thermally grown  $SiO_2$  (100 nm) were used as gate electrodes and gate dielectrics, respectively. After semiconducting NWs were aligned on the substrate, a thermal evaporator was used to deposit Au (100 nm) for the source and drain electrodes. The channel length was  $50 \, \mu m$ .

For inverter fabrication, highly-doped silicon wafer and thermally grown  $SiO_2$  (100 nm) were used as gate electrodes and gate dielectrics, respectively. Inverter electrode patterns of Ti (3 nm) and Au (30 nm) with a channel length of 50  $\mu m$  were thermally deposited on the substrate. N2200:PEO-blend NWs and P3HT:PEO-blend NWs were printed on the pre-patterned substrate.

**ONWL** and nano-channel FETs. Au  $(100\,\mathrm{nm})$  or Ti  $(3\,\mathrm{nm})/\mathrm{Au}$   $(30\,\mathrm{nm})$  or  $\mathrm{Alq_3}$   $(30\,\mathrm{nm})$  was deposited on the aligned PVK NW pattern using a thermal evaporator. PVK NW was removed using adhesive tape or by sonication in a solvent (chloroform or TCE), then the nano-gap metal pattern was formed.

For fabrication of transistors with nanoscale channel length, thermally evaporated Ti (30 nm) on the  $Si/SiO_2$  (100 nm) wafer was used as a gate electrode, and  $Al_2O_3$  (50 nm) served as a gate dielectric, which was formed by atomic layer deposition. ONWL was used to fabricate a nano-gap Au pattern on the substrate for source and drain electrodes. Finally, pentacene (50 nm) was thermally deposited on the nano-gap Au pattern. For the NW and nano-channel transistor, aligned P3HT:PEO-blend NWs were fabricated instead of pentacene.

**P3HT NW FETs with ion-gel dielectric.** ONWL was used to fabricate nano-gap patterns; after PVK NWs were printed on Si/SiO<sub>2</sub> ( $100\,\mathrm{nm}$ ) wafer, Ti ( $3\,\mathrm{nm}$ )/Au ( $30\,\mathrm{nm}$ ) was deposited atop the PVK NWs, which were then removed to form

source and drain electrodes with nano-gap patterns. A P3HT:PEO-blend NW was aligned on the Ti/Au source–drain patterns using ONP. For ion-gel gate dielectric formation, poly(styrene-block-methyl methacrylate-block-styrene) (PS-PMMA-PS) synthesized<sup>31</sup>) triblock copolymer, with block molecular masses  $M_{\rm n}=6.2\,{\rm kg\,mol}^{-1}$  for PS and  $M_{\rm n}=105\,{\rm kg\,mol}^{-1}$  for PMMA, and 1-ethyl-3-methylimidazolium bis(trifluoromethylsulfonyl)imide (solvent innovation) ionic liquid were dissolved in ethyl acetate at a 0.7:9.3:90 ratio (w/w) and then drop-cast onto a P3HT NW pattern that had an Au source and drain contact. After removing the solvent, an ion-gel film was formed by physical association of the PS blocks in the ionic liquid. To form a gate electrode, the substrate was flipped over and placed on a PEDOT:PSS (Baytron P) thin film. PEDOT:PSS layer was clearly transferred to the top surface of the ion-gel.

NW morphology was observed by scanning electron microscope imaging using a Jeol JSM-6330F at an acceleration voltage of 15 kV and by transmission electron microscopy imaging using a JEOL JEM-2200FS (with Cs-corrector) (National Center for Nanomaterials Technology, Korea) at an acceleration voltage of 200 kV without staining. Optical microscope and fluorescence microscope images were recorded using a Zeiss Axioplan 2 optical microscope. 2D GIXRD experiments on P3HT, P3HT:PEO-blend films and arrayed P3HT:PEO-blend NWs on Si substrates were performed at beam line 9A of Pohang Acceleration Laboratory (Korea). The sample was mounted on a two-axis goniometer on top of an x-z stage and the scattered intensity was recorded by a Mar charge-coupled device detector. The incident-beam angle was ca. 0.15° for all 2D GIXRD patterns. Photoluminescence spectra were measured by JASCO FP-6500. Ultraviolet absorption spectra were recorded by ultraviolet-visible spectrophotometer (S-3100, Scinco). The electrical measurements of SiO2-gated devices were conducted under nitrogen atmosphere at room temperature using an I-V tester (Keithley 4200, Keithley Instruments Inc.). The electrical measurements of ion-gel-gated devices were conducted under vacuun condition at room temperature using an I-V tester (Keithley 238 and 6517A, Keithley Instruments Inc.). The dynamic characteristics of NW inverters were measured using a pulse generator (Model 214B, Hewlett-Packard Co.) and a digital oscilloscope (Model 54832B, Agilent Technologies Inc.).

# References

- Kim, D.-H. et al. Stretchable and foldable silicon integrated circuits. Science 320, 507-511 (2008).

- Kang, S. J. et al. High-performance electronics using dense, perfectly aligned arrays of single-walled carbon nanotubes. Nat. Nanotech. 2, 230–236 (2007).

- Sekitani, T. et al. A rubberlike stretchable active matrix using elastic conductors. Science 321, 1468–1472 (2008).

- Duan, X., Huang, Y., Cui, Y., Wang, J. & Lieber, C. M. Indium phosphide nanowires as building blocks for nanoscale electronic and optoelectronic devices. *Nature* 409, 66–69 (2001).

- Takei, K. et al. Nanowire active-matrix circuitry for low-voltage macroscale artificial skin. Nat. Mater. 9, 821–826 (2010).

- Briseno, A. L., Mannsfeld, S. C. B., Jenekhe, S. A., Bao, Z. & Xia, Y. Introducing organic nanowire transistors. *Mater. Today* 11, 38–47 (2008).

- Qiu, L. et al. Organic thin-film transistors based on polythiophene nanowires embedded in insulating polymer. Adv. Mater. 21, 1349–1353 (2009).

- Shi, J., Guo, M. & Li, B. Assembly of arbitrary and vertical optical couplers using flexible polymer micro/nanowires. Appl. Phys. Lett. 93, 121101 (2008).

- Cho, H., Min, S. -Y. & Lee, T. -W. et al. Electrospun Organic Nanofiber Electronics and Photonics. Macromol. Mater. Eng. doi:10.1002/ mame.201200364 (2013).

- Lee, S., Moon, G. D. & Jeong, U. Continuous production of uniform poly (3-hexylthiophene) (P3HT) nanofibers by electrospinning and their electrical properties. J. Mater. Chem. 19, 743–748 (2009).

- Liu, H., Reccius, C. H. & Craighead, H. G. Single electrospun regioregular poly(3-hexylthiophene) nanofiber field-effect transistor. *Appl. Phys. Lett.* 87, 253106 (2005).

- Oh, J. H. et al. Solution-processed, high-performance n-channel organic microwire transistors. Proc. Natl Acad. Sci. USA 106, 6065–6070 (2009).

- Goffri, S. et al. Multicomponent semiconducting polymer systems with low crystallization-induced percolation threshold. Nat. Mater. 5, 950–956 (2006).

- Qin, L., Park, S., Huang, L. & Mirkin, C. A. On-wire lithography. Science 309, 113–115 (2005).

- Liu, S., Tok, J. B. -H. & Bao, Z. Nanowire lithography: fabricating controllable electrode gaps using Au – Ag – Au nanowires. *Nano Lett.* 5, 1071–1076 (2005).

- Colli, A. et al. Nanowire lithography on silicon. Nano Lett. 8, 1358–1362 (2008).

- 17. Park, J. -U. *et al.* High-resolution electrohydrodynamic jet printing. *Nat. Mater.* **6,** 782–789 (2007).

- Reneker, D. H., Yarin, A. L., Fong, H. & Koombhongse, S. Bending instability of electrically charged liquid jets of polymer solutions in electrospinning. J. Appl. Phys. 87, 4531–4547 (2000).

- 19. Sze, S. M. Physics of Semiconductor Devices 2nd edn (Wiley, New York, 1981).

- Ramo, S., Whinnery, J. R. & Duzer, T. V. Fields and Waves in Communication Electronics (Wiley, 1984).

- Chen, Z., Zheng, Y., Yan, H. & Facchetti, A. Naphthalenedicarboximide- vs perylenedicarboximide-based copolymers. synthesis and semiconducting properties in bottom-gate N-channel organic transistors. *J. Am. Chem. Soc.* 131, 8–9 (2009).

- Wei, M., Kang, B., Sung, C. & Mead, J. Core-sheath structure in electrospun nanofibers from polymer blends. *Macromol. Mater. Eng.* 291, 1307–1314 (2006).

- 23. Dimitrakopoulos, C. D. & Malenfant, P. R. L. Organic thin film transistors for large area electronics. *Adv. Mater.* 14, 99–117 (2002).

- Zaumseil, J. et al. Nanoscale organic transistors that use source/drain electrodes supported by high resolution rubber stamps. Appl. Phys. Lett. 82, 793–795 (2003).

- Cho, J. H. et al. Printable ion-gel gate dielectrics for low-voltage polymer thinfilm transistors on plastic. Nat. Mater. 7, 900–906 (2008).

- Panzer, M. J. & Frisbie, C. D. Exploiting ionic coupling in electronic devices: electrolyte-gated organic field-effect transistors. Adv. Mater. 20, 3177–3180 (2008).

- Lee, J. et al. Ion gel-gated polymer thin-film transistors: operating mechanism and characterization of gate dielectric capacitance, switching speed, and stability. J. Phys. Chem. C 113, 8972–8981 (2009).

- Xia, Y., Cho, J. H., Lee, J., Ruden, P. P. & Frisbie, C. D. Comparison of the mobility-carrier density relation in polymer and single-crystal organic transistors employing vacuum and liquid gate dielectrics. *Adv. Mater.* 21, 2174–2179 (2009).

- Xia, Y., Cho, J. H., Paulsen, B., Frisbie, C. D. & Renn, M. J. Correlation of on-state conductance with referenced electrochemical potential in ion gel gated polymer transistors. *Appl. Phys. Lett.* 94, 013304 (2009).

- Briseno, A. L. et al. Perylenediimide nanowires and their use in fabricating field-effect transistors and complementary inverters. Nano Lett. 7, 2847–2853 (2007)

- 31. Hadjichristidis, N., Pispas, S. & Floudas, G. Block Copolymers: Synthetic Strategies, Physical Properties, and Applications (John Wiley and Sons, 2003).

# **Acknowledgements**

This work was supported by a grant (Code No. 2012-0054547) from the Center for Advanced Soft Electronics under the Global Frontier Research Program of the Ministry of Education, Science and Technology, Korea. This research was also supported by the Converging Research Center Program through the Ministry of Education, Science and Technology (No. 2012K001322). We thank Professor J. A. Rogers for helpful comments, Professor Y. C. Kim for kind help in photoluminescence measurement and Ms M. Jang for kind support in graphic design.

#### **Author contributions**

S.-Y.M. conducted most of experiments, including the setup of equipment, development of ONP and ONWL techniques, fabrication of devices and analysis of the data, and prepared the manuscript for the paper. T.-S.K. contributed to the fabrication of NW FETs and analysis of the chain orientation in ONWs using ultaviolet-visible and photoluminescence spectroscopy. B.J.K. and J.H.C. fabricated ion-gel-gated transistors and analysed the data. H.C. contributed to the fabrication of NW FETs and complementary inverters. H.Y. contributed to the analysis of the chain orientation in ONWs using GIXRD. Y.-Y.N. contributed to the fabrication of inverters. T.-W.L. initiated the research, designed all the experiments, analysed all the data and prepared the manuscript. All authors discussed the results and contributed to the paper.

### **Additional information**

Supplementary Information accompanies this paper at http://www.nature.com/naturecommunications

Competing financial interests: The authors declare no competing financial interest.

**Reprints and permission** information is available online at http://npg.nature.com/reprintsandpermissions/

How to cite this article: Min, S. -Y. et al. Large-scale organic nanowire lithography and electronics. Nat. Commun. 4:1773 doi: 10.1038/ncomms2785 (2013).